## ABACUS PERIPHERALS PVT LTD

# ABSNE27-E27T PCIe M.2 2280 KIOXIA BiCS6 Specification (ABSNE271024KP/ABSNE27512KP) (Series - ABSNE27)

Version 1.3

#### **Abacus Peripherals Pvt Ltd**

29,Apurva Indistrial Estate,Makwana Road,Marol,Andheri (E) Mumbai-400059 Tel: +91-22-40914600 Fax: +91-22-40914646

E-mail: daman@abacusperipherals.com

**Document Number: Abacus/SSD/DS/09**

## **REVISION HISTORY**

| Revision | Draft Date | History             |

|----------|------------|---------------------|

| 1.0      | 2024/02/01 | First release       |

| 1.1      | 2024/05/15 | Add series number   |

| 1.2      | 2024/05/15 | Remove 2048GB,256GB |

| 1.3      | 2024/05/20 | Series Correction   |

### **PRODUCT OVERVIEW**

- Capacities

- 512, 1024GB

- Form Factor

- M.2 2280-S2-M

- PCle Interface

- PCle Gen 4 x 4

- Compliance

- NVMe 1.4

- PCI Express Base 4.0

- Flash Interface

- Transfer rate up to 2400MT/s

- Up to 2pcs of BGA154 flash

- Performance<sup>1</sup>

- Read: up to 7400 MB/s

- Write: up to 6400 MB/s

- Reliability

- Mean Time Between Failure (MTBF):

- 1,500,000 hours

- Uncorrectable Bit Error Rate (UBER):

- < 1 sector per 1016 bits read

- Temperature Range<sup>3</sup>

- Operation: 0°C ~ 70°C

- Storage: -40°C ~ 85°C

- Advanced Flash Management

- Dynamic Wear Leveling

- Bad Block Management

- TRIM

- SMART

- Over-Provision

- Firmware Update

- Power Management

- PS0/PS1/PS2/PS3/PS4

- Support APST

- Support ASPM

- Support L1.2

- Power Consumption<sup>2</sup>

- L1.2 < 5mW

- RoHS-Compliant

- Features Support List:

- All SRAM ECC protection

- Thermal throttling

- LDPC + RAID ECC

- SmartRefresh™

- Drive log

- Support HMB (Host Memory Buffer)

- Support of TCG Pyrite

#### NOTES:

- 1. Refer to Chapter 2 for more details

- 2. Refer to Chapter 4, Section for more details.

- 3. The operation temperature means the case temperature, in which can be decided via the S.M.A.R.T.

### **PERFORMANCE**

#### KIOXIA BiCS6 1024Gb TLC (2400MBps)

|          |                 | Sequential   |        | Random       |        | ATTO   |        |

|----------|-----------------|--------------|--------|--------------|--------|--------|--------|

| Conneitu | Flash Structure | (Estimation) |        | (Estimation) |        |        |        |

| Capacity | Flash Structure | Read         | Write  | Read         | Write  | Read   | Write  |

|          |                 | (MB/s)       | (MB/s) | (IOPS)       | (IOPS) | (MB/s) | (MB/s) |

| 512GB    | 256GB x 2, 4CE  | 7200         | 4300   | 530K         | 750K   | 7000   | 5000   |

| 1024GB   | 512GB x 2, 8CE  | 7400         | 6100   | 1000K        | 850K   | 7000   | 5000   |

|          |                 |              |        |              |        |        |        |

#### NOTES:

1. Performance is measured based on the following conditions:

(a) Sequential: CrystalDiskMark 8.0, 1GB range, 5 test count, Q8T1

(b) Random: IOMeter, 1GB range, 4K data size, QD=32T16

(c) ATTO, transfer Size 64MB

(d) CPU: AMD Ryzen 7 5800X 8-Core Processor (e) OS Version: Win10 (64bit), version 1809

(f) Platform: AMD X570

(g) Performance is measured with fresh-out-of-box state SSD storage device.

## **POWER CONSUMPTION**

#### KIOXIA BiCS6 1024Gb TLC (2400MBps)

|          |                          | Power Consumption <sup>1</sup> |       |      |      |

|----------|--------------------------|--------------------------------|-------|------|------|

| Capacity | Flash Configuration      | Read                           | Write | PS3  | PS4  |

|          |                          | (mW)                           | (mW)  | (mW) | (mW) |

| 512GB    | BGA154, KIC BiCS6, DDP*2 | 5150                           | 4300  | 50   | 5    |

| 1024GB   | BGA154, KIC BiCS6, QDP*2 | 5600                           | 5400  | 50   | 5    |

|          |                          |                                |       |      |      |

#### NOTES:

1. Power consumption is measured during the sequential read and write operations performed by IOMeter under ambient temperature @25°C.

## **TABLE OF CONTENTS**

| REV  | 'ISION | N HISTO | RY                                   | . 3 |

|------|--------|---------|--------------------------------------|-----|

| PRC  | DUC    | T OVER\ | /IEW                                 | . 4 |

| PER  | FORM   | MANCE.  |                                      | . 5 |

| PΟ\  | NER (  | CONSUN  | 1PTION                               | . 6 |

| TAB  | LE OF  | CONTE   | NTS                                  | . 7 |

| LIST | OF F   | IGURES  |                                      | . 9 |

| LIST | OF T   | ABLES   |                                      | 10  |

| 1.   | INT    | RODUC   | TION                                 | 11  |

|      | 1.1.   | Ger     | neral Description                    | 11  |

|      | 1.2.   | Cor     | ntroller Block Diagram               | 11  |

|      | 1.3.   | Pro     | duct Block Diagram                   | 12  |

|      | 1.4.   | Flas    | sh Management                        | 12  |

|      |        | 1.4.1.  | Error Correction Code (ECC)          | 12  |

|      |        | 1.4.2.  | Wear Leveling                        | 12  |

|      |        | 1.4.3.  | Bad Block Management                 | 12  |

|      |        | 1.4.4.  | TRIM                                 | 13  |

|      |        | 1.4.5.  | SMART                                | 13  |

|      |        | 1.4.6.  | Over-Provision                       | 13  |

|      |        | 1.4.7.  | Firmware Upgrade                     | 13  |

|      |        | 1.4.8.  | Thermal Throttling                   | 14  |

|      | 1.5.   | Adv     | ranced Device Security Features      | 14  |

|      |        | 1.5.1.  | Secure Erase                         | 14  |

|      |        | 1.5.2.  | Crypto Erase                         | 14  |

|      |        | 1.5.3.  | Physical Presence SID (PSID)         | 14  |

|      | 1.6.   | SSD     | Lifetime Management                  | 14  |

|      |        | 1.6.1.  | Terabytes Written (TBW)              | 14  |

|      |        | 1.6.2.  | Media Wear Indicator                 | 15  |

|      |        | 1.6.3.  | Read Only Mode (End of Life)         | 15  |

|      | 1.7.   | Ada     | ptive Approach to Performance Tuning | 15  |

|      |        | 1.7.1.  | Throughput                           | 15  |

|     | 1                                       | 1.7.2.                                                             | SLC Caching                   | 15 |  |  |

|-----|-----------------------------------------|--------------------------------------------------------------------|-------------------------------|----|--|--|

| 2.  | PROI                                    | OUCT SPEC                                                          | IFICATIONS                    | 16 |  |  |

| 3.  | ENVIRONMENTAL SPECIFICATIONS            |                                                                    |                               |    |  |  |

|     | 3.1.                                    | Environ                                                            | mental Conditions             | 18 |  |  |

|     | ŝ                                       | 3.1.1.                                                             | Temperature and Humidity      | 18 |  |  |

|     | ŝ                                       | 3.1.2.                                                             | Shock                         | 18 |  |  |

|     | 3                                       | 3.1.3.                                                             | Vibration                     | 18 |  |  |

|     | ŝ                                       | 3.1.4.                                                             | Drop                          | 19 |  |  |

|     | ŝ                                       | 3.1.5.                                                             | Bending                       | 19 |  |  |

|     | ŝ                                       | 3.1.6.                                                             | Durability                    | 19 |  |  |

|     | ŝ                                       | 3.1.7.                                                             | Electrostatic Discharge (ESD) | 19 |  |  |

|     | 3                                       | 3.1.8.                                                             | EMI Compliance                | 19 |  |  |

|     | 3.2.                                    | MTBF                                                               |                               | 19 |  |  |

|     | 3.3.                                    | Certific                                                           | ation & Compliance            | 20 |  |  |

| 4.  | ELEC                                    | TRICAL SPE                                                         | ECIFICATIONS                  | 21 |  |  |

|     | 4.1.                                    | Supply                                                             | Voltage                       | 21 |  |  |

|     | 4.2.                                    | Power (                                                            | Consumption                   | 21 |  |  |

| 5.  | INTE                                    | RFACE                                                              |                               | 23 |  |  |

|     | 5.1.                                    | Pin Assi                                                           | ignment and Descriptions      | 23 |  |  |

| 6.  | SUPP                                    | ORTED CO                                                           | DMMANDS                       | 26 |  |  |

|     | 6.1.                                    | NVMe/                                                              | ATA Command List              | 26 |  |  |

|     | 6.2.                                    | Identify                                                           | Device Data                   | 27 |  |  |

|     | 6.3.                                    | SMART                                                              | Attributes                    | 30 |  |  |

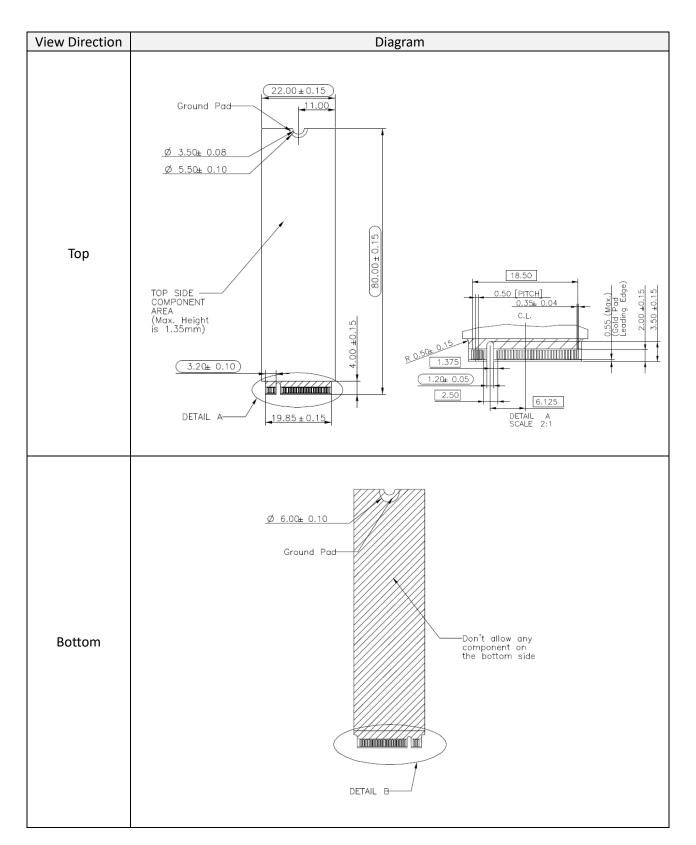

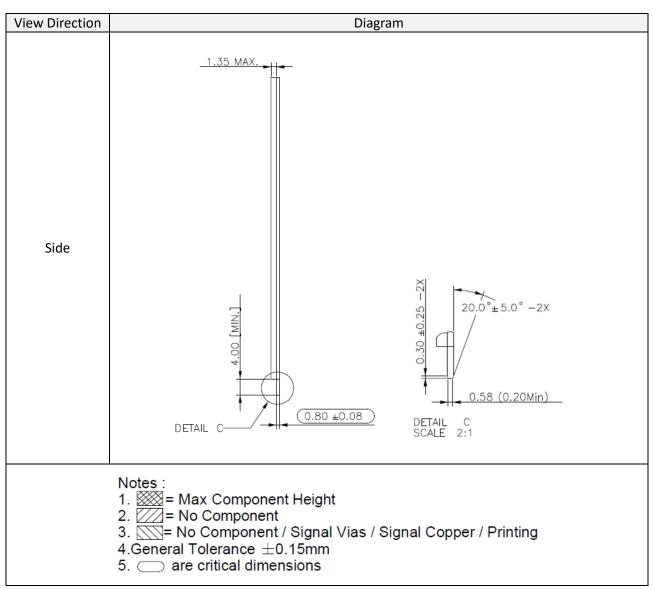

| 7.  | PHYS                                    | SICAL DIME                                                         | ENSION                        | 31 |  |  |

| 8.  | APPL                                    | ICATION N                                                          | IOTES                         | 33 |  |  |

|     | 8.1.                                    | 8.1. Wafer Level Chip Scale Packaging (WLCSP) Handling Precautions |                               |    |  |  |

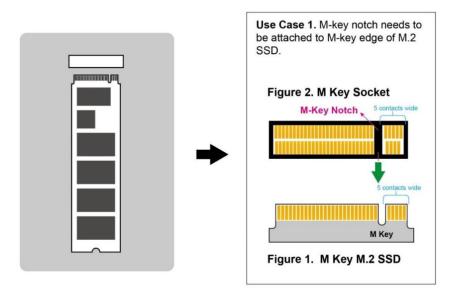

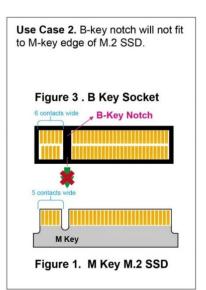

|     | 8.2. M Key M.2 SSD Assembly Precautions |                                                                    |                               |    |  |  |

| 9.  | REFERENCES                              |                                                                    |                               |    |  |  |

| 10. | . TERMINOLOGY35                         |                                                                    |                               |    |  |  |

| 11  | DR∩I                                    | NICT WAR                                                           | RANTY POLICY                  | 36 |  |  |

## **LIST OF FIGURES**

| Figure 1-1 PS5027-E27T Controller Block Diagram       | . 11 |

|-------------------------------------------------------|------|

| Figure 1-2 PS5027-E27T M.2 2280 Product Block Diagram | . 12 |

| Figure 7-1 Product Mechanical Diagram and Dimensions  | . 32 |

| Figure 8-1 M Key M.2 Assembly Precautions             | . 33 |

## **LIST OF TABLES**

| Table 2-1 TBW of PS5027-E27T+KIOXIA BiCS6                             | 17 |

|-----------------------------------------------------------------------|----|

| Table 3-1 High Temperature                                            | 18 |

| Table 3-2 Low Temperature                                             | 18 |

| Table 3-3 High Humidity                                               | 18 |

| Table 3-4 Temperature Cycling                                         | 18 |

| Table 3-5 Shock                                                       | 18 |

| Table 3-6 Vibration                                                   | 18 |

| Table 3-7 Drop                                                        | 19 |

| Table 3-8 Bending                                                     | 19 |

| Table 3-9 Durability                                                  | 19 |

| Table 3-10 ESD                                                        | 19 |

| Table 3-11 EMI                                                        | 19 |

| Table 3-12 Certification & Compliance                                 | 20 |

| Table 4-1 Supply Voltage                                              | 21 |

| Table 4-2 Power Consumption with KIOXIA BiCS6 1024Gb (2400) TLC in mW | 21 |

| Table 5-1 Pin Assignment and Description of PS5027-E27T M.2 2280      | 23 |

| Table 6-1 Admin Commands                                              | 26 |

| Table 6-2 Admin Commands – NVM Command Set Specific                   | 26 |

| Table 6-3 NVM Commands                                                | 26 |

| Table 6-4 Identify Controller Data Structure                          | 27 |

| Table 6-5 SMART Attributes (Log Identifier 02h)                       | 30 |

| Table 9-1 List of Standards References                                | 34 |

| Table 10-1 List of Terminology                                        | 35 |

### 1. INTRODUCTION

#### 1.1. General Description

PS5027-E27T M.2 2280 with no external DDR solution delivers all the advantages of flash disk technology with PCIe Gen4 x4 interface and is fully compliant with the standard Next Generation Form Factor (NGFF) called M.2 Card Format. PS5027-E27T M.2 2280 offers a wide range of capacities up to 1024GB and its performance can reach up to 7400 MB/s<sup>1</sup> and 6400 MB/s<sup>1</sup> based on KIC BiCS6 1024Gb TLC NAND flash. NOTES:

1. Achieved by 1024GB SSD at FOB (fresh-out-of-box) state on CrystalDiskMark v8.0.

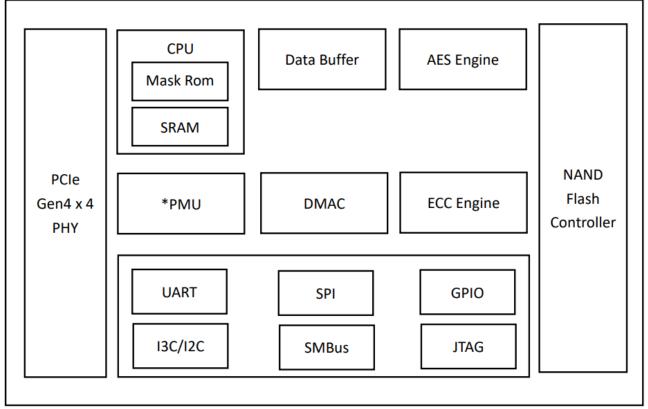

### 1.2. Controller Block Diagram

<sup>\*</sup>PMU = Power Management Unit

Figure 1-1 PS5027-E27T Controller Block Diagram

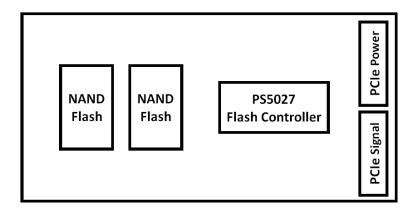

#### 1.3. Product Block Diagram

Figure 1-2 PS5027-E27T M.2 2280 Product Block Diagram

#### 1.4. Flash Management

#### 1.4.1. Error Correction Code (ECC)

Flash memory cells will deteriorate with use, which might generate random bit errors in the stored data. Thus, PS5027-E27T PCIe SSD applies the LDPC (Low Density Parity Check) of ECC algorithm, which can detect and correct errors occur during read process, ensure data been read correctly, as well as protect data from corruption.

#### 1.4.2. Wear Leveling

NAND flash devices can only undergo a limited number of program/erase cycles, when flash media is not used evenly, some blocks get updated more frequently than others and the lifetime of device would be reduced significantly. Thus, wear leveling is applied to extend the lifespan of NAND flash by evenly distributing write and erase cycles across the media.

Abacus provides advanced wear leveling algorithm, which can efficiently spread out the flash usage through the whole flash media area. Moreover, by implementing both dynamic and static wear leveling algorithms, the life expectancy of the NAND flash is greatly improved.

#### 1.4.3. Bad Block Management

Bad blocks are blocks that do not function properly or contain more invalid bits causing stored data unstable, and their reliability is not guaranteed. Blocks that are identified and marked as bad by the manufacturer are referred to as "Early Bad Blocks". Bad blocks that are developed during the lifespan of the flash are named

"Later Bad Blocks". Abacus implements an efficient bad block management algorithm to detect the factory-produced bad blocks and manages bad blocks that appear with use. This practice prevents data being stored into bad blocks and further improves the data reliability.

#### 1.4.4. TRIM

TRIM is a feature which helps improve the read/write performance and speed of solid state drives (SSD). Unlike hard disk drives (HDD), SSDs are not able to overwrite existing data, so the available space gradually becomes smaller with each use. With the TRIM command, the operating system can inform the SSD so that blocks of data that are no longer in use can be removed permanently. Thus, the SSD will perform the erase action, which prevents unused data from occupying blocks at all time.

#### 1.4.5. SMART

SMART, an acronym for Self-Monitoring, Analysis and Reporting Technology, is an open standard that allows a solid state drive to automatically detect its health and report potential failures. When a failure is recorded by SMART, users can choose to replace the drive to prevent unexpected outage or data loss. Moreover, SMART can inform users impending failures while there is still time to perform proactive actions, such as save data to another device.

#### 1.4.6. Over-Provision

Over Provisioning refers to the preserving additional area beyond user capacity in a SSD, which is not visible to users and cannot be used by them. However, it allows a SSD controller to utilize additional space for better performance and WAF. With Over Provisioning, the performance and IOPS (Input/output Operations per Second) are improved by providing the controller additional space to manage P/E cycles, which enhances the reliability and endurance as well. Moreover, the write amplification of the SSD becomes lower when the controller writes data to the flash.

#### 1.4.7. Firmware Upgrade

Firmware can be considered as a set of instructions on how the device communicates with the host. Firmware will be upgradable when new features are added, compatibility issues are fixed, or read/write performance gets improved.

#### 1.4.8. Thermal Throttling

The purpose of thermal throttling is to prevent any components in a SSD from over-heating during read and write operations. PS5027-E27T is designed with an on-die thermal sensor and with its accuracy; firmware can apply different levels of throttling to achieve the purpose of protection efficiently and proactively via SMART reading.

#### 1.5. Advanced Device Security Features

#### 1.5.1. Secure Erase

Secure Erase is a standard NVMe format command and will write all "0x00" to fully wipe all the data on hard drives and SSDs. When this command is issued, SSD controller will erase its storage blocks and return to its factory default settings.

#### 1.5.2. Crypto Erase

Crypto Erase is a feature that erases all data of an OPAL-activated SSD or a "SED" (Security-Enabled Disk) drive by resetting the cryptographic key of the disk. Since the key is modified, the previously encrypted data will become useless, achieving the purpose of data security.

#### 1.5.3. Physical Presence SID (PSID)

Physical Presence SID (PSID) is defined by TCG OPAL as a 32-character string and the purpose is to revert SSD back to its manufacturing setting when the drive is still OPAL-activated. PSID code can be printed on a SSD label when an OPAL-activated SSD supports PSID revert feature.

#### 1.6. SSD Lifetime Management

#### 1.6.1. Terabytes Written (TBW)

TBW (Terabytes Written) is a measurement of SSDs' expected lifespan, which represents the amount of data written to the device. To calculate the TBW of a SSD, the following equation is applied:

$TBW = [(NAND \ Endurance) \times (SSD \ Capacity)] / [WAF]$

NAND Endurance: NAND endurance refers to the P/E (Program/Erase) cycle of a NAND flash.

SSD Capacity: The SSD capacity is the specific capacity in total of a SSD.

<u>WAF</u>: Write Amplification Factor (WAF) is a numerical value representing the ratio between the amount of data that a SSD controller needs to write and the amount of data that the host's flash controller writes. A

better WAF, which is near 1, guarantees better endurance and lower frequency of data written to flash memory.

TBW in this document is based on JEDEC 219 workload.

#### 1.6.2. Media Wear Indicator

Actual life indicator reported by SMART Attribute byte index [5], Percentage Used, recommends User to replace drive when reaching to 100%.

#### 1.6.3. Read Only Mode (End of Life)

When drive is aged by cumulated program/erase cycles, media worn-out may cause increasing numbers of later bad block. When the number of usable good blocks falls outside a defined usable range, the drive will notify Host through AER event and Critical Warning to enter Read Only Mode to prevent further data corruption. User should start to replace the drive with another one immediately.

### 1.7. Adaptive Approach to Performance Tuning

#### 1.7.1. Throughput

Based on the available space of the disk, PS5027-E27T will regulate the read/write speed and manage the performance of throughput. When there still remains a lot of space, the firmware will continuously perform read/write action. There is still no need to implement garbage collection to allocate and release memory, which will accelerate the read/write processing to improve the performance. Contrarily, when the space is going to be used up, PS5027-E27T will slow down the read/write processing, and implement garbage collection to release memory. Hence, read/write performance will become slower.

#### 1.7.2. SLC Caching

PS5027-E27T's firmware design currently adopts dynamic caching to deliver better performance for better endurance and consumer user experience.

## 2. PRODUCT SPECIFICATIONS

- Capacity

- 512GB, 1024GB

- Support 32-bit addressing mode

- Electrical/Physical Interface

- PCle Interface

- Compliant with NVMe 1.4

- PCle Express Base Version 4.0

- PCIe Gen 4 x 4 lane & backward compatible to PCIe Gen 3, PCIe Gen 2 and Gen

1

- Support up to QD 128 with queue depth of up to 64K

- Support power management

- Supported NAND Flash

- Support up to 16 Flash Chip Enables (CE) within a single design

- Support up to 2pcs of BGA154 flash

- Support 8-bit I/O NAND Flash

- Support Toggle5.0 interface

- ECC Scheme

- PS5027-E27T PCIe SSD applies LDPC + RAID ECC algorithm.

- Sector Size Support

- 512B

- 4KB

- UART/ GPIO

- Support SMART and TRIM commands

- LBA Range

- IDEMA standard

#### ■ TBW (Terabytes Written)

Table 2-1 TBW of PS5027-E27T+KIOXIA BiCS6

| Capacity | TBW     |

|----------|---------|

| 512GB    | >300 TB |

| 1024GB   | >600 TB |

|          |         |

#### ■ Performance

#### KIOXIA BiCS6 1024Gb TLC (2400MBps)

|          |                 | Sequential |        | Random |        |

|----------|-----------------|------------|--------|--------|--------|

| Capacity | Flash Structure | Read       | Write  | Read   | Write  |

|          |                 | (MB/s)     | (MB/s) | (IOPS) | (IOPS) |

| 512GB    | 256GB x 2, 4CE  | 7200       | 4300   | 530K   | 750K   |

| 1024GB   | 512GB x 2, 8CE  | 7400       | 6100   | 1000K  | 850K   |

|          |                 |            |        |        |        |

#### NOTES:

1. Performance is measured based on the following conditions:

(a) Sequential: CrystalDiskMark 8.0, 1GB range, 5 test count, Q8T1

(b) Random: IOMeter, 1GB range, 4K data size, QD=32T16

(c) CPU: AMD Ryzen 7 5800X 8-Core Processor (d) OS Version: Win10 (64bit), version 1809

(e) Platform: AMD X570

(f) Performance is measured with fresh-out-of-box state SSD storage device.

## 3. ENVIRONMENTAL SPECIFICATIONS

#### 3.1. Environmental Conditions

#### 3.1.1. Temperature and Humidity

#### Table 3-1 High Temperature

|           | Temperature | Humidity |

|-----------|-------------|----------|

| Operation | 70°C        | 0% RH    |

| Storage   | 85°C        | 0% RH    |

#### Table 3-2 Low Temperature

|           | Temperature | Humidity |

|-----------|-------------|----------|

| Operation | 0°C         | 0% RH    |

| Storage   | -40°C       | 0% RH    |

#### Table 3-3 High Humidity

|           | Temperature | Humidity |

|-----------|-------------|----------|

| Operation | 40°C        | 90% RH   |

| Storage   | 40°C        | 93% RH   |

#### Table 3-4 Temperature Cycling

|           | , , ,       |  |  |

|-----------|-------------|--|--|

|           | Temperature |  |  |

| Operation | 0°C         |  |  |

| Operation | 70°C¹       |  |  |

| Characa   | -40°C       |  |  |

| Storage   | 85°C        |  |  |

#### Notes:

1. The operation temperature is measured by the case temperature, in which can be decided via the S.M.A.R.T. Airflow is suggested and it will allow device to be operated at appropriate temperature for each component during heavy workloads environment.

#### 3.1.2. Shock

#### Table 3-5 Shock

|                 | Acceleration Force |

|-----------------|--------------------|

| Non-operational | 1500G              |

#### 3.1.3. Vibration

#### Table 3-6 Vibration

|                 | Condition                                     |                 |  |  |

|-----------------|-----------------------------------------------|-----------------|--|--|

|                 | Frequency/Displacement Frequency/Acceleration |                 |  |  |

| Non-operational | 20Hz~80Hz/1.52mm                              | 80Hz~2000Hz/20G |  |  |

#### 3.1.4. Drop

#### Table 3-7 Drop

|                 | Height of Drop | Number of Drop      |

|-----------------|----------------|---------------------|

| Non-operational | 80cm free fall | 6 face of each unit |

#### *3.1.5. Bending*

#### Table 3-8 Bending

| <u> </u>        |       |                  |  |  |

|-----------------|-------|------------------|--|--|

|                 | Force | Action           |  |  |

| Non-operational | ≥ 20N | Hold 1min/5times |  |  |

#### 3.1.6. Durability

#### Table 3-9 Durability

|             | Condition          |

|-------------|--------------------|

| operational | 1000 mating cycles |

#### 3.1.7. Electrostatic Discharge (ESD)

#### Table 3-10 ESD

| Specification                  | +/- 4KV                                                              |

|--------------------------------|----------------------------------------------------------------------|

| EN 55024, CISPR 24             | Device functions are affected, but EUT will be back to its normal or |

| EN 61000-4-2 and IEC 61000-4-2 | operational state automatically.                                     |

#### 3.1.8. EMI Compliance

#### Table 3-11 EMI

|                        | Specification |

|------------------------|---------------|

| EN 55032, CISPR 32(CE) |               |

| AS/NZS CISPR 32(CE)    |               |

| ANSI C63.4 (FCC)       |               |

| VCCI-CISPR 32 (VCCI)   |               |

| CNS 13438 (BSMI)       |               |

#### 3.2. MTBF

MTBF, Mean Time Between Failures, is a measure of reliability of a device. Its value represents the average time between a repair and the next failure. The unit of MTBF is in hours. The higher the MTBF value, the higher the reliability of the device.

Our MTBF result is based on Telcordia methodology. Please note that a lower MTBF should be expected for higher capacity drives, and we apply the lowest MTBF for all capacities.

### 3.3. Certification & Compliance

Table 3-12 Certification & Compliance

| Specification            |  |  |

|--------------------------|--|--|

| RoHS                     |  |  |

| WHQL                     |  |  |

| PCI Express Base 4.0     |  |  |

| UNH-IOL NVM Express Logo |  |  |

### 4. ELECTRICAL SPECIFICATIONS

#### 4.1. Supply Voltage

Table 4-1 Supply Voltage

| Parameter                  | Rating          |  |  |  |

|----------------------------|-----------------|--|--|--|

| Operating Voltage          | Min = 3.14V     |  |  |  |

| Operating Voltage          | Max = 3.47 V    |  |  |  |

| Rise Time (Max/Min)        | 100 ms / 0.1 ms |  |  |  |

| Fall Time (Max/Min)        | 5 s / 1 ms      |  |  |  |

| Min. Off Time <sup>1</sup> | 5 s             |  |  |  |

#### NOTE:

1. Minimum time between power removed from SSD (Vcc < 100 mV) and power re-applied to the drive.

#### 4.2. Power Consumption

Table 4-2 Power Consumption with KIOXIA BiCS6 1024Gb (2400) TLC in mW

| Canacity | Capacity Flash Configuration    | CE# | Read |      | Write |      |

|----------|---------------------------------|-----|------|------|-------|------|

| Сараспу  |                                 |     | Max. | Avg. | Max.  | Avg. |

| 512GB    | BGA154, KIC BiCS6 1024Gb, DDP*2 | 4   | TBD  | TBD  | TBD   | TBD  |

| 1024GB   | BGA154, KIC BiCS6 1024Gb, QDP*2 | 8   | TBD  | TBD  | TBD   | TBD  |

|          |                                 |     |      |      |       |      |

#### NOTES:

- 1. Power consumption is measured with the condition under ambient temperature @25°C.

- 2. The average value of power consumption is achieved based on 100% conversion efficiency.

- 3. The measured power voltage is 3.3V.

Table 4-3 Power State Power Consumption with KIOXIA BiCS6 1024Gb (2400) TLC in mW

| Canacity | Flash Configuration CE#         | CE# | Active |      |      | PS3 | PS4 |

|----------|---------------------------------|-----|--------|------|------|-----|-----|

| Capacity |                                 | CE# | PS0    | PS1  | PS2  | P35 | F34 |

| 512GB    | BGA154, KIC BiCS6 1024Gb, DDP*2 | 4   | 5150   | 3000 | 1700 | 50  | 5   |

| 1024GB   | BGA154, KIC BiCS6 1024Gb, QDP*2 | 8   | 5600   | 3000 | 1800 | 50  | 5   |

|          |                                 |     |        |      |      | _   |     |

#### NOTES:

- 4. Power consumption is measured with the condition under ambient temperature @25°C.

- 5. The average value of power consumption is achieved based on 100% conversion efficiency.

- 6. The measured power voltage is 3.3V.

- 7. The temperature of a storage device in PS1 should remain constant or should slightly decrease for all workloads so the actual power in PS1 should be lower than PS0.

- 8. The temperature of a storage device in PS2 should decrease sharply for all workloads so the actual power in PS2 should be lower than PS1.

- 9. PS3 & PS4 is specific in L1.2

#### Table 4-4 Mobile Mark 2023 Average Power Consumption with KIOXIA BiCS6 1024Gb (2400) TLC in mW

| Capacity | Flash Structure | CE# | Primary |

|----------|-----------------|-----|---------|

| 512GB    | 256GB x 2 BiCS6 | 4   | TBD     |

| 1024GB   | 512GB x 2 BiCS6 | 8   | TBD     |

|          |                 |     |         |

#### NOTES:

- 1. Power consumption is measured with the condition under ambient temperature @25°C.

- 2. The average value of power consumption is achieved based on 100% conversion efficiency.

- 3. The measured power voltage is 3.3V.

## 5. INTERFACE

### 5.1. Pin Assignment and Descriptions

Table 5-1 defines the signal assignment of the internal NGFF connector for SSD usage, described in the PCI Express M.2 Specification version 1.0 of the PCI-SIG.

Table 5-1 Pin Assignment and Description of PS5027-E27T M.2 2280

|         | 10010 0 21 1117 1001611  | The first and Description of 1 33027 2271 W. 2 2200                   |  |

|---------|--------------------------|-----------------------------------------------------------------------|--|

| Pin No. | PCIe Pin                 | Description                                                           |  |

| 1       | GND                      | Return current path.                                                  |  |

| 2       | 3.3V PWR_1 source        |                                                                       |  |

| 3       | GND                      | Return current path.                                                  |  |

| 4       | 3.3V                     | PWR_1 source                                                          |  |

| г       | DET <sub>2</sub> 2       | PCIe TX/RX Differential signals defined by the                        |  |

| 5       | PETn3                    | PCI Express Base Specification.                                       |  |

|         |                          | Active high with weak pull-down on                                    |  |

| 6       | PWRDIS (I)(0/1.8/3.3V)   | Adapters. Power Disable notifies the                                  |  |

|         |                          | Adapter to disable the power on the Adapter.                          |  |

| 7       | DETn2                    | PCIe TX/RX Differential signals defined by the                        |  |

| ,       | PETp3                    | PCI Express Base Specification.                                       |  |

|         |                          | Power Loss Notification. Open drain with a pull-up on Adapters        |  |

|         |                          | that support power loss notification. When the Platform               |  |

| 8       | DI N# (IVO/1 9/2 2V/)    | supports power loss notification, this signal is asserted to indicate |  |

| 8       | PLN# (I)(0/1.8/3.3V)     | a power loss event is expected to occur. When the                     |  |

|         |                          | Adapter supports this function and the                                |  |

|         |                          | signal is asserted then it must ready itself for power loss.          |  |

| 9       | GND                      | · · · · · · · · · · · · · · · · · · ·                                 |  |

|         |                          | Open drain, active low signal. This signal is used to allow the       |  |

| 10 LEI  | LED_1# (O)(OD)           | Adapter to provide status indication via LED device that will be      |  |

|         |                          | provided by the system.                                               |  |

| 11      | DED~2                    | PCIe TX/RX Differential signals defined by the                        |  |

| 11      | PERn3                    | PCI Express Base Specification.                                       |  |

| 12      | 3.3V PWR_1 source        |                                                                       |  |

| 13      | DED <sub>D</sub> 2       | PCIe TX/RX Differential signals defined by the                        |  |

| 15      | PERp3                    | PCI Express Base Specification.                                       |  |

| 14      | 3.3V                     | PWR_1 source                                                          |  |

| 15      | GND                      | Return current path.                                                  |  |

| 16      | 3.3V                     | PWR_1 source                                                          |  |

| 17      | DETag                    | PCIe TX/RX Differential signals defined by the                        |  |

| 17      | PETn2                    | PCI Express Base Specification.                                       |  |

| 18      | 3.3V                     | PWR_1 source                                                          |  |

| 10      | DET-2                    | PCIe TX/RX Differential signals defined by the                        |  |

| 19      | PETp2                    | PCI Express Base Specification.                                       |  |

| 20      | NC No connect            |                                                                       |  |

| 21      | GND Return current path. |                                                                       |  |

| 22      | VIO 1.8V                 | I/O source (low current)                                              |  |

|         |                          | PCIe TX/RX Differential signals defined by the                        |  |

| 23      | PERn2                    | PCI Express Base Specification.                                       |  |

| 24      | NC                       | No connect                                                            |  |

|         |                          | •                                                                     |  |

| PERP2 PERP2 PCIE TX/RX Differential signals defined by the PCI Express Base Specification.  No connect  Return current path. No connect  PCIE TX/RX Differential signals defined by the PCIE Spress Base Specification.  PERP1 PCIE TX/RX Differential signals defined by the PCIE Spress Base Specification.  PERP1 PCIE TX/RX Differential signals defined by the PCIE Spress Base Specification.  PERP1 PCIE TX/RX Differential signals defined by the PCIE Spress Base Specification. An Adapter that support that support power loss notification. An Adapter that support that support power loss processing complete state.  PCIE TX/RX Differential signals defined by the PCIE Spress Base Specification.  PERP1 PCIE TX/RX Differential signals defined by the PCIE Spress Base Specification.  PERP1 PCIE TX/RX Differential signals defined by the PCIE Spress Base Specification.  PERP1 PCIE TX/RX Differential signals defined by the PCIE Spress Base Specification.  PERP1 PCIE TX/RX Differential signals defined by the PCIE Spress Base Specification.  PERP1 PCIE TX/RX Differential signals defined by the PCIE Spress Base Specification.  SMB_CLK (I/O)(0/1.8V) SMBus clock. Open Drain with pull up on Platform PCIE TX/RX Differential signals defined by the PCIE TX | Pin No. | PCle Pin                                                                                                                                        | Description                                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|

| 26 NC No connect 27 GND Return current path. 28 NC No connect 29 PETn1 PCLE TX/RX Differential signals defined by the PCLE XPRSS Base Specification.  POWER LOSS ACKNOWLEDGE. Open drain with pull-up on Platform that support power loss notification. An Adapter that support this function, must drive the signal to reflect its current power loss processing complete state.  31 PETp1 PCLE TX/RX Differential signals defined by the PCLE XPRSS Base Specification. 32 GND Return current path. 33 GND Return current path. 34 NC No connect 35 PERn1 PCLE TX/RX Differential signals defined by the PCLE XPRSS Base Specification. 36 NC No connect 37 PERp1 PCLE TX/RX Differential signals defined by the PCLE XPRSS Base Specification. 38 GND Return current path. 39 GND Return current path. 40 SMB_CLK (I/O)(IO/1.8V) SMBus clock. Open Drain with pull up on Platform PCLE XPRSS Base Specification. 41 PETn0 PCLE TX/RX Differential signals defined by the PCLE XPRSS Base Specification. 42 SMB_DATA (I/O)(IO/1.8V) SMBus data. Open Drain with pull up on Platform PCLE XPRSS Differential signals defined by the PCLE XPRSS Base Specification.  44 ALERT#(I) (IO/1.8V) PCLE TX/RX Differential signals defined by the PCLE XPRSS Base Specification.  45 GND Return current path.  46 NC No connect  47 PERn0 PCLE TX/RX Differential signals defined by the PCLE XPRSS Base Specification.  48 NC No connect  49 PERP0 | 25      | PERp2                                                                                                                                           |                                                                   |

| 27 GND Return current path. 28 NC No connect 29 PETn1 PCIE TX/RX Differential signals defined by the PCI Express Base Specification. 30 PLA_S3# (O)(0/1.8/3.3V) 30 PLA_S3# (O)(0/1.8/3.3V) 31 PETp1 PCIE TX/RX Differential signals defined by the PCI Express Base Specification. 31 PETp1 PCIE TX/RX Differential signals defined by the PCI Express Base Specification. 32 GND Return current path. 33 GND Return current path. 34 NC No connect 35 PERn1 PCIE TX/RX Differential signals defined by the PCI Express Base Specification. 36 NC No connect 37 PERp1 PCIE TX/RX Differential signals defined by the PCI Express Base Specification. 38 GND Return current path. 39 GND Return current path. 39 GND Return current path. 40 SMB_CLK (I/O)(0/1.8V) SMBus clock. Open Drain with pull up on Platform 41 PETn0 PCIE TX/RX Differential signals defined by the PCI Express Base Specification. 42 SMB_DATA (I/O)(0/1.8V) SMBus data. Open Drain with pull up on Platform 43 PETp0 PCIE TX/RX Differential signals defined by the PCI Express Base Specification. 44 ALERT#(O) (0/1.8V) SMBus data. Open Drain with pull up on Platform 45 GND Return current path. 46 NC No connect 47 PERn0 PCIE TX/RX Differential signals defined by the PCI Express Base Specification. 48 NC No connect 47 PERn0 PCIE TX/RX Differential signals defined by the PCI Express Base Specification. 48 NC No connect 49 PERp0 PCIE TX/RX Differential signals defined by the PCI Express Base Specification. 50 PERST# (I)(0/1.8V) SMBus data. Open Drain with pull up on Platform PCIE TX/RX Differential signals defined by the PCIE TX/R |         | ·                                                                                                                                               |                                                                   |

| 28 NC PETN1 POWER LOSS Acknowledge. Open drain with pull-up on Platform that support power loss notification. An Adapter that support this function, must drive the signal to reflect its current power loss processing complete state.  31 PETP1 POWER LOSS Acknowledge. Open drain with pull-up on Platform that support power loss notification. An Adapter that support this function, must drive the signal to reflect its current power loss processing complete state.  31 PETP1 POWER LOSS Acknowledge. Open drain with pull-up on Platform that support power loss notification. An Adapter that support this function, must drive the signal to reflect its current power loss processing complete state.  32 GND Return current path. 33 GND Return current path. 34 NC No connect  35 PERN1 PCIE TX/RX Differential signals defined by the PCIE TX/RX Differential signals defined by the PCIE Express Base Specification. 36 NC No connect  37 PERP1 PCIE TX/RX Differential signals defined by the PCIE Express Base Specification. 38 GND Return current path. 39 GND Return current path. 40 SMB_CLK (I/O)(0/1.8V) SMBus clock. Open Drain with pull up on Platform PCIE TX/RX Differential signals defined by the PCIE Express Base Specification. 41 PETN0 PCIE TX/RX Differential signals defined by the PCIE Express Base Specification. 42 SMB_DATA (I/O)(0/1.8V) SMBus data. Open Drain with pull up on Platform PCIE TX/RX Differential signals defined by the PCIE TX/RX Differential signals defined by the PCIE TX/RX Differential signals defined by the PCIE Express Base Specification. 44 ALERT#(O) (0/1.8V) Alert notification to initiator. Open Drain with pull up on Platform. Active Low PCIE TX/RX Differential signals defined by the PCIE TX/RX Differential signals defined by the PCIE Express Base Specification. 45 GND Return current path. 46 NC No connect 47 PERN0 PCIE TX/RX Differential signals defined by the PCIE Express Base Specification. 48 NC Roconnect 49 PERP0 PCIE TX/RX Differential signals defined by the PCIE Express Base Specification. 49 PCIE Express Base |         |                                                                                                                                                 |                                                                   |

| PETN1 POWER LOSS Acknowledge. Open drain with pull-up on Platform that support power loss notification. An Adapter that support this function, must drive the signal to reflect its current power loss processing complete state.  PETP1 PETP1 PETP1 PICE TX/RX Differential signals defined by the PCI Express Base Specification.  PETP1 PETP1 PICE TX/RX Differential signals defined by the PCI Express Base Specification.  PETP1 PICE TX/RX Differential signals defined by the PCI Express Base Specification.  PERN1 PERN1 PICE TX/RX Differential signals defined by the PCI Express Base Specification.  PERN1 PERP1 PICE TX/RX Differential signals defined by the PCI Express Base Specification.  PERP1 PICE TX/RX DIFFERENTIAL SIGNAL PROBLEM PICE Express Base Specification.  PETP1 PICE TX/RX DIFFERENTIAL SIGNAL PROBLEM PICE Express Base Specification.  SMB_CLK (I/O)(0/1.8V) SMBus clock. Open Drain with pull up on Platform PCI Express Base Specification.  PETP0 PCI EXPRX DIFFERENTIAL SIGNAL SIGNAL PROBLEM PICE Express Base Specification.  ALERT#(O) (0/1.8V) SMBus data. Open Drain with pull up on Platform PCI Express Base Specification.  ALERT#(O) (0/1.8V) ALERT#(O) PCI EXPRESS Base Specification.  ALERT#(O) PERN0 PCI EXPRESS Base Specification.  ALERT#(O) PERN0 PCI EXPRESS Base Specification.  PCI Express Base Specification.  ALERT#(D) PCI EXPRESS Base Specification.  PCI Express Base |         |                                                                                                                                                 | -                                                                 |

| PCI Express Base Specification.  Power Loss Acknowledge. Open drain with pull-up on Platform that support power loss notification. An Adapter that support this function, must drive the signal to reflect its current powe loss processing complete state.  PCIE TX/RX Differential signals defined by the PCI Express Base Specification.  Return current path.  Return current path.  Return current path.  PCIE TX/RX Differential signals defined by the PCI Express Base Specification.  PERN1 PCIE TX/RX Differential signals defined by the PCI Express Base Specification.  PCIE TX/RX Differential signals defined by the PCI Express Base Specification.  PERN1 PCIE TX/RX Differential signals defined by the PCI Express Base Specification.  Return current path.  Return current path.  SMB_CLK (I/O)(0/1.8V) SMBus clock. Open Drain with pull up on Platform PCI Express Base Specification.  PETN0 PCIE TX/RX Differential signals defined by the PCI Express Base Specification.  PETN0 PCIE TX/RX Differential signals defined by the PCI Express Base Specification.  ALERT#(O) (0/1.8V) SMBus data. Open Drain with pull up on Platform PCIE TX/RX Differential signals defined by the PCI Express Base Specification.  ALERT#(O) (0/1.8V) Alert notification to initiator. Open Drain with pull up on Platform PCIE TX/RX Differential signals defined by the PCI Express Base Specification.  ALERT#(D) PERN0 PCIE TX/RX Differential signals defined by the PCI Express Base Specification.  PERN0 PCIE TX/RX Differential signals defined by the PCI Express Base Specification.  PERN0 PCIE TX/RX Differential signals defined by the PCI Express Base Specification.  PERN0 PCIE TX/RX Differential signals defined by the PCI Express Base Specification.  PCIE TX/RX Differential signals defined by the PCI Express Base Specification.  PCIE TX/RX Differential signals defined by the PCI Express Base Specification.  PCIE TX/RX Differential signals defined by the PCI Express Base Specification.  PCIE TX/RX Differential signals defined by the PCI Express Base Specification.  PCIE T | 28      | NC                                                                                                                                              |                                                                   |

| PCI Express Base Specification.  PLA_S3# (O)(0/1.8/3.3V)  PLA_S3# (O)(0/1.8/3.3V)  PETp1  PETp1  PETp1  PCIE TX/RX Differential signals defined by the PCI Express Base Specification.  PERp1  PCI Express Base Specification.  PETp1  PETp1  PCI Express Base Specification.  Return current path.  PCI Express Base Specification.  PERp1  PCI Express Base Specification.  PERp1  PCI Express Base Specification.  PCI Express Base Specification.  PERp1  PCI Express Base Specification.  PCI Express Base Specification.  Return current path.  PCI Express Base Specification.  Return current path.  SMB_CLK (I/O)(0/1.8V)  SMBus clock. Open Drain with pull up on Platform  PCI Express Base Specification.  PCI Express Base Specification.  PCI Express Base Specification.  PETp0  PCI Express Base Specification.  ALERT#(O) (0/1.8V)  ALERT#(O) (0/1.8V)  ALERT#(O) (0/1.8V)  PERp0  PCI Express Base Specification.  PCI Express Base Specif | 29      | PETn1                                                                                                                                           |                                                                   |

| that support power loss notification. An Adapter that support this function, must drive the signal to reflect its current powe loss processing complete state.  31 PETp1 PCIE TX/RX Differential signals defined by the PCI Express Base Specification.  32 GND Return current path.  33 GND Return current path.  34 NC No connect  35 PERn1 PCIE TX/RX Differential signals defined by the PCI Express Base Specification.  36 NC No connect  37 PERp1 PCIE TX/RX Differential signals defined by the PCI Express Base Specification.  38 GND Return current path.  39 GND Return current path.  39 GND Return current path.  40 SMB_CLK (I/O)(0/1.8V) SMBus clock. Open Drain with pull up on Platform  41 PETn0 PCIE TX/RX Differential signals defined by the PCI Express Base Specification.  42 SMB_DATA (I/O)(0/1.8V) SMBus data. Open Drain with pull up on Platform  43 PETp0 PCIE TX/RX Differential signals defined by the PCI Express Base Specification.  44 ALERT#(O) (0/1.8V) Alert notification to initiator. Open Drain with pull up on Platform Active Low  45 GND Return current path.  46 NC No connect  47 PERn0 PCIE TX/RX Differential signals defined by the PCI Express Base Specification.  48 NC No connect  49 PERp0 PCIE TX/RX Differential signals defined by the PCI Express Base Specification.  50 PERST# (I)(0/1.8V/3.3V) PCIE TX/RX Differential signals defined by the PCI Express Base Specification.  50 PERST# (I)(0/1.8V/3.3V) PCIE TX/RX Differential signals defined by the PCI Express Base Specification.  51 GND Return current path.  52 PCIE TX/RX Differential signals defined by the PCI Express Base Specification.  53 PCIE Reset is a functional reset to the card a defined by the PCI Express Base Specification.  54 PCIE Clock Request is a reference clock request signal as defined by the PCIE content as  |         |                                                                                                                                                 |                                                                   |

| 31 PEIp1 PCI Express Base Specification.  32 GND Return current path.  33 GND Return current path.  34 NC No connect  35 PERn1 PCI Express Base Specification.  36 NC NC No connect  37 PERp1 PCI Express Base Specification.  38 GND Return current path.  39 GND Return current path.  40 SMB_CLK (I/O)(0/1.8V) SMBus clock. Open Drain with pull up on Platform  41 PETn0 PCI Express Base Specification.  42 SMB_DATA (I/O)(0/1.8V) SMBus data. Open Drain with pull up on Platform  43 PETp0 PCI Express Base Specification.  44 ALERT#(O) (0/1.8V) Alert notification to initiator. Open Drain with pull up on Platform. Active Low  45 GND Return current path.  46 NC No connect  47 PERn0 PCI Express Base Specification.  48 NC No connect  49 PERp0 PCI Express Base Specification.  Alert notification to initiator. Open Drain with pull up on Platform PCI Express Base Specification.                                                                                                                                                                                                                                                               | 30      | PLA_S3# (O)(0/1.8/3.3V) that support power loss notification. An Adapter that sup this function, must drive the signal to reflect its current p |                                                                   |

| 32   GND   Return current path.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 31      | PETp1                                                                                                                                           |                                                                   |

| 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 32      | GND                                                                                                                                             |                                                                   |

| 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |                                                                                                                                                 |                                                                   |

| PERN1   PCIe TX/RX Differential signals defined by the PCI Express Base Specification.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |                                                                                                                                                 | •                                                                 |

| PERN1   PCI Express Base Specification.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |                                                                                                                                                 | PCIe TX/RX Differential signals defined by the                    |

| 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 35      | PERn1                                                                                                                                           |                                                                   |

| SMB_CLK (I/O)(0/1.8V)   SMBus clock. Open Drain with pull up on Platform                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 36      | NC                                                                                                                                              |                                                                   |

| PERP1   PCI Express Base Specification.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         | 252.4                                                                                                                                           | PCIe TX/RX Differential signals defined by the                    |

| 38 GND Return current path. 39 GND Return current path. 40 SMB_CLK (I/O)(0/1.8V) SMBus clock. Open Drain with pull up on Platform 41 PETnO PCIE TX/RX Differential signals defined by the PCI Express Base Specification. 42 SMB_DATA (I/O)(0/1.8V) SMBus data. Open Drain with pull up on Platform 43 PETpO PCIE TX/RX Differential signals defined by the PCI Express Base Specification. 44 ALERT#(O) (0/1.8V) Alert notification to initiator. Open Drain with pull up on Platform. Active Low 45 GND Return current path. 46 NC No connect 47 PERnO PCIE TX/RX Differential signals defined by the PCI Express Base Specification. 48 NC No connect 49 PERpO PCIE TX/RX Differential signals defined by the PCI Express Base Specification. 50 PERST# (I)(0/1.8V/3.3V) PERST# (I)(0/1.8V/3.3V) STANDARD RETURN CURRENT DIFFERENTIAL SIGNAL SEGMENT DIFFERENT DI | 37      | PERp1                                                                                                                                           |                                                                   |

| 40 SMB_CLK (I/O)(0/1.8V) SMBus clock. Open Drain with pull up on Platform  PETn0 PCIE TX/RX Differential signals defined by the PCI Express Base Specification.  42 SMB_DATA (I/O)(0/1.8V) SMBus data. Open Drain with pull up on Platform  PCIE TX/RX Differential signals defined by the PCI Express Base Specification.  ALERT#(O) (0/1.8V) PCIE TX/RX Differential signals defined by the PCI Express Base Specification.  Alert notification to initiator. Open Drain with pull up on Platform. Active Low  ALERT#(O) (0/1.8V) Return current path.  NC No connect  PCIE TX/RX Differential signals defined by the PCI Express Base Specification.  NO connect  PCIE TX/RX Differential signals defined by the PCI Express Base Specification.  PCIE TX/RX Differential signals defined by the PCI Express Base Specification.  PCIE Reset is a functional reset to the card as defined by the PCI Express BaseSpecification.  Return current path.  PCIE Clock Request is a reference clock request signal as defined price as defined by the PCI Express BaseSpecification.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 38      | GND                                                                                                                                             |                                                                   |

| PETn0 PETn0 PCIE TX/RX Differential signals defined by the PCI Express Base Specification.  PETp0 PCIE TX/RX Differential signals defined by the PCI Express Base Specification.  PETp0 PCIE TX/RX Differential signals defined by the PCI Express Base Specification.  ALERT#(O) (0/1.8V) ALERT#(O) (0/1. | 39      | GND                                                                                                                                             | Return current path.                                              |

| PETn0 PETn0 PCIE TX/RX Differential signals defined by the PCI Express Base Specification.  42 SMB_DATA (I/O)(0/1.8V) SMBus data. Open Drain with pull up on Platform  43 PETp0 PCIE TX/RX Differential signals defined by the PCI Express Base Specification.  44 ALERT#(O) (0/1.8V) Alert notification to initiator. Open Drain with pull up on Platform. Active Low  45 GND Return current path.  46 NC No connect  47 PERn0 PCIE TX/RX Differential signals defined by the PCI Express Base Specification.  48 NC No connect  49 PERp0 PCIE TX/RX Differential signals defined by the PCI Express Base Specification.  50 PERST# (I)(0/1.8V/3.3V) PCIE Reset is a functional reset to the card as defined by the PCI Express BaseSpecification.  51 GND Return current path.  PCIE Clock Request is a reference clock request signal as defined price and provided the point of the point o | 40      |                                                                                                                                                 |                                                                   |